# Neuro-Fuzzy Buck Boost Converter Implement on FPGA

Radhika M. Jaju<sup>1</sup>, Nilesh N. Kasat<sup>2</sup>

M.E. (IInd Year), EXTC Department, SIPNA COET Amravati, M.S., India 1 Associate Professor, EXTC Department, SIPNA COET Amravati, M.S., India<sup>2</sup>

**Abstract:** The DC-DC power converters are widely used. However, the controller design for DC-DC power converters cannot easily design if load is dynamics vary widely. Therefore a Field Programmable Gate Array (FPGA) is proposed to build a neuro fuzzy system for controlling a nonlinear buck boost converter. A Very High speed integrated circuit Hardware Description Language (VHDL) has been used to implement the proposed controller. The main purpose behind implementation of the NF controller in VHDL is to minimize the hardware implementation cost of the generic NF controller for use in industrial applications. Xilinx ISE 13.1 program has been used as programming environment to type and synthesis the VHDL codes that described the neuro-fuzzy controller and to generate a configuration file which is used to program the FPGA board.

Keywords: Buck-Boost converter, FPGA, Neuro-Fuzzy Control, VHDL

# I. INTRODUCTION

This paper aims to establish the superior performance of neuro fuzzy controllers at various structure-learning algorithm to find appropriate Fuzzy logic rules and use then parameter-learning algorithm to fine-tune membership function and other parameters. The proposed controller reveals that it is adaptive for all operating conditions. Simulation results are shown and settling time and peak overshoot have been used to measure the performance.

The requirement for short time-to-market has devices very popular implementation of general purpose electronic devices. Modern FPGA architectures offer the advantage of partial reconfiguration, which allows an algorithm to be partially mapped into a small and fixed FPGA device that can be reconfigured at run time, as the mapped application changes its requirements. Such a feature can be beneficial for modern control applications that may require the change of coefficients, models and control laws with respect to external conditions. The proposed solution is both technically advanced and cost effective, offering flexibility, modularity and efficiency, without performance reduction Traditional frequency

domain methods for design of controllers for power converters are based on small signal model of the

operating points of the buck & boost converters. The converter. The small signal model of the converter basic concept of Neuro-Fuzzy control method is first has restricted validity and changes due to changes in operating point. Also the models are not sufficient to represent systems with strong non-linearity. A state space averaged model of the classical Buck boost DC/DC converters suffers from the well known problem of Right-Half-Plane zero in its control to output transfer function under continuous conduction mode. There are two possible routes to achieve fast dynamic response. One way is to develop a more accurate non-linear model of the converter based on which the controller is designed. The other way is the artificial intelligence way of using human experience in decision-making. Among the various techniques of artificial intelligence, the most popular and widely used technique in control systems is the fuzzy logic. Such an intelligent controller designed may even work well with a system with an approximate model.

### II. BACKGROUND

# A. Linearized Model for Buck Boost Converter

The Buck-Boost converter is a type of step-down and step-up DC-DC converter. Output of the Buck-Boost converter is regulated according to the duty cycle of the PWM input at fixed frequency. When the duty cycle (d) is less than 0.5, the output voltage of converter is lower than the input voltage. On other condition, when the duty cycle is more than 0.5 the

Copyright to IJIREEICE www.ijireeice.com

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 2, Issue 1, January 2014

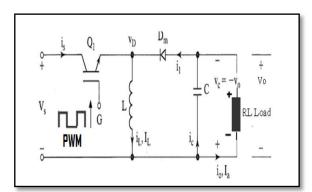

output voltage of converter is higher than the input voltage. The basic circuit of a Buck-Boost converter source, Vo is output voltage, SW is switching output voltage is derived as follow component, d is diode, C is capacitance, L is inductor windings and **R** is load resistance..

Figure 1: Buck Boost Converter

The equivalent equations for Buck-Boost converter during switching-on can be derived as follow: When D where d is duty cycle are given as the switch is ON, the diode is open

$$v_I = v_S \tag{1}$$

$$v_l = L \left( \frac{di_l}{dt} \right)$$

Substitions of (1) and (2)

$$v_s = L\left(\frac{di_l}{dt}\right) \tag{3}$$

$$\Delta i_{l(close)} = \frac{v_s DT}{L}$$

(4)

When the switch is OFF, the diode is closed

$$v_l = v_0$$

$$v_L = L\left(\frac{di_l}{dt}\right)$$

Substitutions of (5) and (6)

$$L\left(\frac{di_l}{dt}\right) = v_o \tag{7}$$

$$\Delta i_{l(open)} = \frac{-v_o(1-D)T}{L}$$

(8)

Where D is duty cycle.

In steady state operation by solving the linear is illustrated in Fig.1 where VI is input voltage equation during turn-on and turn-off the average

$$\Delta i_{l(open)} + \Delta i_{l(close)} = 0$$

$$\frac{v_S DT}{L} + \frac{v_O (1 - D)T}{L} = 0$$

$$\frac{v_O(1-D)T}{L} = \frac{-v_S DT}{L}$$

$$v_o = -v_S \frac{D}{1-D} \tag{9}$$

To develop a dynamic model of the Buck-Boost converter, a state space averaging model is applied. In this method the averaging state space formula of the converter during turn-on and turn-off with D'=1-

$$\dot{X} = AX + BU \tag{10}$$

$$Y = CX \tag{11}$$

$$X = \begin{bmatrix} i_L \\ v_C \end{bmatrix}$$

$$U = v_1$$

$$Y = v$$

$$A = \begin{bmatrix} 0 & \frac{D'}{L} \\ \frac{-D'}{C} & \frac{-1}{RC} \end{bmatrix}$$

$$(5) B = \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix}$$

$$(6) C = \begin{bmatrix} 0 & 1 \end{bmatrix}$$

The transfer function of the Buck-Boost converter in the continuous system is finally found as

$$G(s) = \frac{-D'R}{LRCs^2 + Ls + D'^2R}$$

# B. Neuro Fuzzy Design procedure:

The design of Neuro Fuzzy controller needs a good

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 2, Issue 1, January 2014

knowledge of the system operation. The various steps involved in the design of Neuro Fuzzy controller for power converter are stated below. A universal 3. Development of rule base: Sugeno type Neuro Fuzzy controller has been simulated for the buck converter.

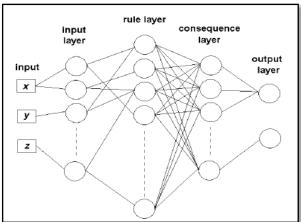

Figure 2: Stucture of Designed NeuroFuzzy

# 1. Identification of inputs and outputs:

This step in the design identifies the key inputs that generic logic cells and programmable switches that affect the system performance. The goal of the designer is to ensure that the output voltage matches the reference voltage. The inputs to the Neuro Fuzzy controller are

- i. The voltage error.

- ii. The change of voltage error.

the form of inductor current. The voltage error input is sampled once in every cycle. The output of the controller is the incremental control action i.e. the incremental duty ratio.

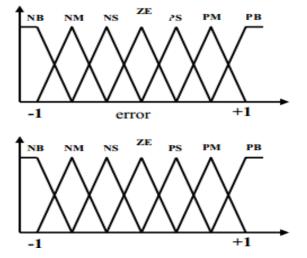

# 2. Fuzzifying the inputs and outputs:

The universe of discourse of the inputs is divided into seven fuzzy sets of triangular shapes. Outputs singletons.

Figure 3: Membership Function

The rules connecting the inputs and the output singletons are based on the understanding of the system. Normally the fuzzy rules have if...then... structure. The inputs are combined by AND operator. The rule-base contains the fuzzy IF-THEN rules of sugeno's first order type.

# **4.** Defuzzification:

The fuzzy conclusion values are mapped to crisp outputs .The output space with the singletons is 'defuzzified' to get a final crisp value of the incremental control, in which the output of each rule is a linear combination of input variables plus a constant term.

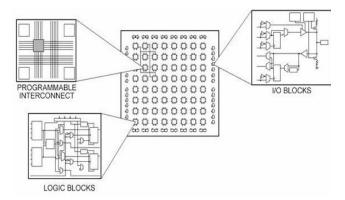

# C. FPGA

A field programmable gate array (FPGA) is a logic device that contains a two-dimensional array of can realize any digital system with low cost and reduced time. The FPGA consists of three major configurable elements

- 1) Configurable Logic Block (CLBs) arranged in an array that provides the functional elements and Some controllers even may use more information in implements most of the logic in an FPGA. Each logic block has two flip flops and it can realize any 5-input combination logic function.

- 2) Programmable Interconnect Resources (PIRs) that provides a routing path to connect between the rows and columns of CLBs, and between CLBs and inputoutput blocks.

- are also mapped into several fuzzy regions of several 3) Input-Output Blocks (IOBs) that provide the interface between the package pins and internal signal lines. It can be configured as an input, output or bidirectional port. The CLBs, IOBs and their interconnectors are controlled by a configuration program store in a chip memory.

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 2, Issue 1, January 2014

Figure 4: Architecture of FPGA

### FPGA Process:

- 1. Architecture design. This stage involves analysis of the project requirements, problem decomposition and functional simulation (if applicable). The output of this stage is a document which describes the future device architecture, structural blocks, their functions and interfaces.

- 2. HDL design entry. The device is described in a formal hardware description language (HDL). The most common HDLs are VHDL and Verilog.

- 3. Behavioral simulation. : The simulator software verifies the functionality and timing of your design or portion of your design. The simulator interprets VHDL or Verilog code into circuit functionality and displays logical results of the described HDL to determine correct circuit operation. Simulation allows you to create and verify complex functions in a relatively small amount of time.

- 4. Synthesis. During synthesis, the synthesis engine compiles the design to transform HDL sources into an architecture-specific design net list. Synthesis decreases design time by eliminating the need to define every gate. During HDL synthesis, XST analyzes the HDL code and attempts to infer specific design building blocks or macros (such as MUXs, RAMs, adders, and subtractors) for which it can create efficient technology implementations.

- 5. Implementation. After synthesis, you run design implementation, which converts the logical design into a physical file format that can be downloaded to the selected target device.

- 6. Timing analysis. During the timing analysis special software checks whether the implemented design satisfies timing constraints (such as clock frequency) specified by the user.

Figuure 5: Flow chat of FPGA

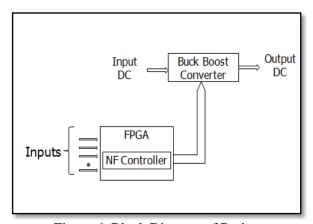

# D. Proposed block Diagram

Figure 6: Block Diagram of Project

Figure shows the proposed hardware behavior of neuro fuzzy logic control that will be design VHDL language & implement on Xilinx Spartan 3E FPGA board. First, a VHDL codes are downloaded from the host computer into the FPGA chip using a USB cable. Then, Edge connector is used to interface the board (NF controller) with model of the buck boost converter. The digital input with switches has been applied as input data to the FPGA boards. The FPGA board generates the digital inputs to the NF controller. The NF controller generates a suitable digital control signal based on the rules that were stored in the FPGA chip. The digital control signals generate pulse waveform and pulse waveform will be applied as an input to the buck boost converter. At the same time buck boost converter also get DC input supply. Thus at the output we get DC output.

# III. CONCLUSION

The buck boost converters are subjected to various disturbances of input voltage and load changes is performed to demonstrate the effectiveness of the INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 2, Issue 1, January 2014

proposed controller. The conclusions drawn from the results are

- I. The proposed novel controller gives small overshoots and has much superior performance compared to the local PI controllers.

- II. The Neuro-Fuzzy controller behaves effectively like an adaptive local tuned controller designed for each operating point and gives an improved performance compared to the conventional PI controller.

- III. The proposed Neuro-Fuzzy controller is adaptive for all the operating point as compared to Fuzzy controller.

### REFRENCES

- 1) S. Joseph Jawhar1, N.S. Marimuthu2, S.K Pillai3 and N. Albert Singh, Neuro-Fuzzy Controller for a Non Linear Power Electronic Buck & Boost Converters, Asian Power Electronics Journal, Vol. 1, Aug 2007

- Feshk Farahani, Designing & Implementation of a

Fuzzy Controller for DC-DC Converters& comparing With PI Digital Controller, Australian Journal of Basic and Applied Sciences, 2011

- 3)Fazel Taeed, Zainal Salam, Member, IEEE, Shahrin M. Ayob Member, IEEE," FPGA Implementation of a Single-Input Fuzzy Logic Controller for Boost Converter With the Absence of an External Analog-to-Digital Converter", FEBRUARY 2012.

- 4) Kamarposhti M A, Tayebbifar, Derafshi Kh, Shaker SH, Nouri P. The Control of Buck Boost DC-DC Converters for DC Motor Drives on variable DC Voltage by Using Neural Network.

- 5) Biranchinath Sahu, Student Member, IEEE, and Gabriel A. Rincon-Mora, Senior Member, IEEE, A Low Voltage, Dynamic, Non inverting, Synchronous Buck-Boost Converter for Portable Applications, VOL. 19, NO. 2, MARCH 2004

- 6) FATHI SHABAN JABER, DEVELOPMENT OF A DC-DC BUCK BOOST CONVERTER USING FUZZY LOGIC CONTROL,2011.

- 7) Kamel Ben Saad, Abdelaziz Sahbani and Mohamed Benrejeb Research unit LARA, National engineering school of Tunis (ENIT), Tunis, Tunisia, "Sliding Mode Control and Fuzzy Sliding Mode Control for DC-DC Converters"

- 8) P. J. Werbos, "Neurocontrol and Nerofuzzy logic: connections and design," Int. J. Approximate Reasoning, Vol. 6, Feb. 1992, pp. 185-220.

- 9) LIN P.Z., LIN C.M., HSU C.F., LEE T.T. (2006): Type-2 fuzzy controller design using sliding-model approach for application to DC-DC converters', IEE Proc. Electrower, 152.

- 10) Inés del Campo, *Associate Member, IEEE*, Javier Echano be, *Member, IEEE*, Guillermo Bosque, and

- José Manuel Tarela," Efficient Hardware/Software Implementation of an Adaptive Neuro-Fuzzy System", JUNE 2008

- 11) Wing-Chi So; Dept. of Electron. Eng., Hong Kong Polytechnic. Univ., Hong Kong; C.K.; Lee, Y.-S., Development of a fuzzy logic controller for DC/DC converters: design, computer simulation, and experimental evaluation.