INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING

# SPARSE MATRIX CONVERTER FED INDUCTION DRIVE USING FUZZY LOGIC CONTROLLER

# Dr.T.Govindaraj<sup>1</sup>, N.Saranya<sup>2</sup>

Prof&Head, Department of EEE, Muthayammal Engineering College, Rasipuram, India<sup>1</sup> PG Shcolar, Department of EEE, Muthayammal Engineering College, Rasipuram, India<sup>2</sup>

**Abstract:** In this project, quasi network based sparse matrix converter and a compensation method based on a fuzzy logic controller to compensate the input voltage. The structure of an SMC to reduce the number of unipolar power semiconductor switches employs a quasi network to overcome the inherent limitation of the low voltage transfer ratio of conventional matrix converters. Although the SMC is a two-stage converter, it directly connects between a source and a load through a quasi network, which is designed to have smaller passive components as the only purpose is voltage boosting. The operational principle of the SMC is described and its modulation strategy is explained. Simulation results are shown to verify the feasibility of the SMC and its operation.

Index Terms: Sparse Matrix Converter, Quasi Network, Compensation, Fuzzy Logic Control.

### **I.INTRODUCTION**

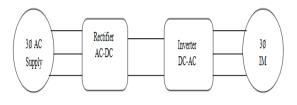

Matrix converter is capable of direct conversion from AC to AC by using bidirectional fully controlled switches. In ac-ac power conversion, two types of conversion systems are used. They are ac-dc-ac two stage conversion system and the other is an ac-ac-ac one stage direct conversion system. The traditional indirect converter produces variable-amplitude and/or frequency output voltages with a stiff dc-link voltage that is acquired by a larger dc-link energy-storage component, such as an electrolytic capacitor. Unlike the traditional indirect converter, the direct converter connects any input phase to any output phase with an array of controlled power semiconductor switches without the dc-link energy-storage component. This type of converter is called as matrix converter[1].

The matrix converters can be implemented with two different topologies: one is a direct matrix converter and the other is an indirect matrix converter shown in Fig. 1. The structure of the direct matrix converter is based on direct ac-ac power conversion by coupling the input and output sides with nine bidirectional switches, while the indirect matrix converter is based on ac-dc-ac power without dc-link conversion any energy-storage component[2]. Although the direct and indirect matrix converters differ with respect to the circuit configuration, control strategy, efficiency, and complexity, they provide similar basic functionalities, such as sinusoidal input currents and bidirectional power flow with the same number of unipolar power semiconductor switches[3]. Since a matrix converter connects a source and a load without any energy-storage component, its output voltage can only be synthesized directly with input line-to-line voltages. Under this restriction, the maximum output voltage that the matrix converter can produce without entering the over modulation range is equal to 86% of the maximum input voltage.

Fig. 1. Matrix converter

For electrical drive applications, it means that a derated motor or a nonstandard motor is required. Furthermore, disturbances at the input source are immediately reflected to the load. The unbalanced input voltages can result in unwanted output harmonic currents and the short-time input-voltage sag can bring the voltage sag on the load. These can deteriorate the performance of the load[3]-[5],[12]-[22].

# II. QUASI NETWORK

The quasi z-source inverter (QZSI) is a single stage power converter derived from the Z-source inverter topology, employing a unique impedance network. The conventional VSI and CSI suffer from the limitation that triggering two switches in the same leg or phase leads to a source short and in addition, the maximum obtainable output voltage cannot exceed the dc input, since they are buck converters and can produce a voltage lower than the dc input voltage. Both Z-source inverters and quasi-Z-source inverters overcome these drawbacks, by utilizing several shoot-through zero states. A zero state is produced when the upper three or lower three switches are fired simultaneously to boost the output voltage. Sustaining the

### INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL. ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 2, Issue 1, January 2014

states can be partially or completely replaced by the shoot bidirectional flow of the dc-link current. through states depending upon the voltage boost requirement. Quasi-Z-source inverters (QZSI) acquire all B. RECTIFIER STAGE impedance network couples the source and the inverter to achieve voltage boost and inversion in a single stage. By using this new topology, the inverter draws a constant current from the PV array and is capable of handling a wide input voltage range. It also features lower component ratings, reduces switching ripples to the PV panels, causes less EMI problems and reduced source stress compared to the traditional ZSI.

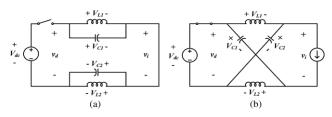

The QZSI circuit differs from that of a conventional ZSI in the LC impedance network interface between the source and inverter. The unique LC and diode network connected to the inverter bridge modify the operation of the circuit, allowing the shoot-through state which is forbidden in traditional VSI. This network will effectively protect the circuit from damage when the shoot through occurs and by using the shoot-though state, the (quasi-) Z-source network boosts the dc-link voltage. The Quasi network consists of inductors and capacitors connected as shown in fig. This network is employed to provide an impedance source, coupling the converter to the load. The dc source can be a battery, diode rectifier, thyristor converter or PV array. The QZSI topology is shown in the Fig. 2.

Fig. 2. Equivalent circuit of the quasi Z-source inverter (a) Shoot through state mode (b) Nonshoot-through state mode

# A. OPERATION

The ZSMC mainly operates in two different operating modes one is a shoot-through state mode, in which the energy is charged in the Z-source network, and the other is a non shoot-through state mode (or a normal operating mode), in which the stored energy is used to synthesize the output voltages. If it is assumed that the Z-source inverter is fed by a constant dc-link voltage during one switching period, two equivalent circuits for each of these operating mode During the shoot-through state mode T0, the Zsource inverter stage is intentionally short circuited and the dc-link switch S1 is opened, which separates the dclink from the rectifier stage. During this period, the rectification stage performs the commutation as mentioned earlier. The shoot through can be achieved in seven different ways: short circuit of any one phase leg, any two phase legs, or all three phase legs. This produces a shoot through zero state in which the energy is charged in the Zsource network. During the non shoot-through state mode T1, the Z-source inverter operates as a normal inverter

six permissible active switching states of a VSI, the zero and the dc-link switch S1 is closed, which will allow the

the advantages of traditional Z-source inverter. The In order to ensure proper operation of the ZSMC, a dclink voltage should always be positive and the bidirectional current flow capability of the rectifier stage should be achieved by using bidirectional switches. The rectifier stage of the ZSMC can commutate with zero dclink current when the Z-source inverter is in the shootthrough zero state. Therefore, the rectifier stage has only to ensure that no short circuit of an input line-to-line voltage occurs. In order to make a maximum dc-link voltage available to form the output voltage, the input phase with the highest absolute value is clamped to the positive or negative dc-link bus voltage according to its polarity.

## C. INVERTER STAGE

A modified SVPWM algorithm with a shoot-through capability can be used for the Z-source inverter stage, In order to ensure zero-current switching in the rectifier stage, the inverter is switched into the shoot-through zero state, and then, the rectifier stage commutates with zero current. The shoot-through zero state can be inserted in the middle of a free-wheeling state (zero vector).

It should be noted that each phase leg switches ON and OFF two times per switching period without changing the total time of a free-wheeling state. The active states are thereby unchanged. However, the equivalent dc-link voltage to the inverter is boosted by the shoot-through zero state.

# D. INDUCTOR DESIGN

During traditional operation mode, the capacitor voltage is always equal to the input voltage. So there is no voltage across the inductor. During shoot through mode, the inductor current increases linearly and the voltage across the inductor is equal to the voltage across the capacitor. The average current through the inductor is given by, IL = P/Vdc (3.11). Where P is the total power and Vdc is the input voltage. The average current at 1kW and 150 V input is IL (avg) = 1000/150 = 6.67A. The maximum current occurs through the inductor when the maximum shootthrough happens, which causes maximum ripple current. In this design, 30% current ripple through the inductors during maximum power operation was chosen. Therefore the allowed ripple current was 4A and maximum current is 10.67A. For a switching frequency of 10 kHz, the average capacitor voltage is VC = (1-TO/T) \* Vdc / (1-2TO/T)Substituting the values in the above equation the average capacitor voltage is 300V. So the inductance is L = 0.1 \*10 \* 300 / 10.67 = 3mH

# E. CAPACITOR DESIGN

The purpose of the capacitor is to absorb the voltage ripple and maintain a fairly constant voltage. During shootthrough the capacitor charges the inductors and the current through the capacitor equals the current in the inductor. Therefore the voltage ripple across the capacitor is VC = IL(avg)TS/C (3.13). The capacitor voltage ripple is 0.17%.

### INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 2, Issue 1, January 2014

capacitance was found to be C = 6.67 \* 0.1 \* 10 (300 \*0.0017) =  $1000\mu$ F Hence the impedance network of the Quasi Z-Source inverter consists of a inductor of value 3mH and capacitor of 1000µF.

# III. COMPENSATION METHOD BASED ON FLC

Although the ZSMC is a two-stage converter, it directly connects a source and a load with a Z-source network, which is designed to have passive components only for the purpose to boost the output voltage. Therefore, if the input voltages of the ZSMC are unbalanced, the dc-link voltage is directly affected. The output voltages synthesized with the distorted dc-link volt- age are also distorted, which will cause undesirable harmonics in the output currents of the ZSMC. The grid usually suffers the steady state and transient voltage unbalanced problems, which are caused by various factors in the transmission and distribution networks. These problems are difficult to predict and to estimate. An FLC is basically a nonlinear adaptive controller so that it can give robust performance for both linear and nonlinear systems. Therefore, it is attractive in a ZSMC and may have better performance than a traditional PI controller under these distorted and unpredictable conditions. This paper introduces an FLC-based outputcurrent- compensation method.

### A.FLC

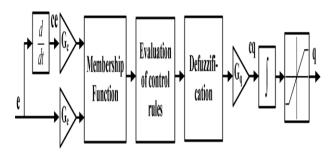

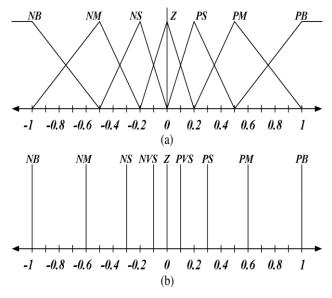

The FLC is fed by the instantaneous error e of  $I_0$  and produces a voltage transfer ratio q for the Z-source inverter. With this voltage transfer ratio, the Z-source inverter can synthesize proper output voltages that will control a constant  $I_0$ . The FLC uses the error e and the change of error "ce" as input as shown in Fig. 3. The instantaneous value of the error can be obtained by subtracting a reference current space vector  $I_{re}$  f from the measured output current space vector and calculated. The change of error is the difference between the present and previous values of the error. These inputs are converted per-unit signals by multiplying corresponding scaling factors  $G_e$  and  $G_c$ . With these perunit input values, a fuzzification process is performed using the triangular membership functions shown in Fig. 4(a). Asymmetrical triangular membership functions have been selected in this design, which causes crowding near the origin and, therefore, gives more precision near the origin. The universe of discourse for input variables e(pu) and ce(pu) spreads in the region from -1 to +1 and the membership functions are symmetrical on both positive and negative sides. The evaluation of control rules is performed with the rules shown in Table I. The top row and left column describe the sets for the input variables e(pu) and ce(pu), respectively. Because there are seven sets by for each input variable, there are in total 49 rules in Table I. The defuzzification is carried out using singleton membership functions as shown in Fig. 4(b), which is usually called the zero-order Sugeno method of implication. The output of the FLC system is the change of voltage transfer ratio "cq" and its universe of discourse is between -1 to +1 as well. The actual voltage transfer

Substituting the above values in the equation the required ratio q can be obtained by integrating the change of voltage gain after multiplying with a proper scaling factor  $G_q$ . For a conventional matrix converter, a saturation block is needed for the FLC system because it has the inherent limitation of the voltage transfer ratio with the maximum value. However the Quasi ZSMC can theoretically have any value from zero to infinity as a voltage transfer ratio. Nevertheless, for an actual implementation, the maximum voltage transfer ratio of the Quasi ZSMC is also restricted by the size of the inductors and capacitors in the Z-source network another hardware ratings.

Fig. 3. Block diagram of FLC

Fig. 4. Membership function for (a) fuzzification (b) defuzzification

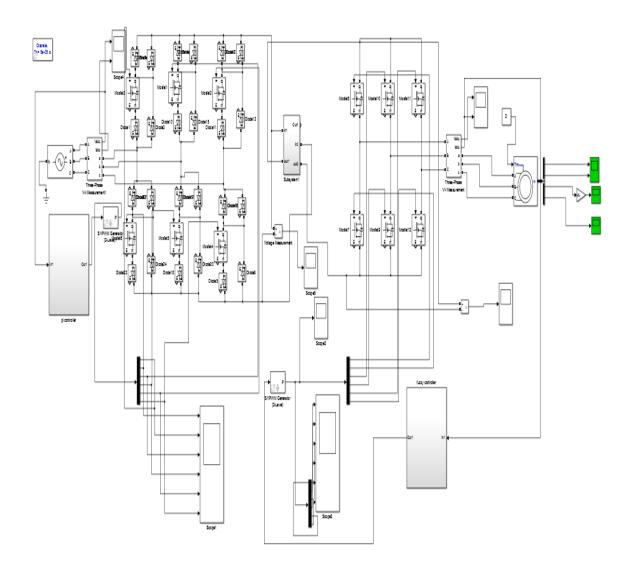

### IV. SIMULATION

Using MATLAB simulation have been done to verify the output performance of the matrix converter using the compensation method. MATLAB stands for "Matrix Laboratory" and is a numerical computing environment and fourth-generation programming language. Developed MathWorks, MATLAB allows the matrix multiplications, plotting of functions implementation of algorithms, creation of users interfaces and interfacing with programs written in other languages including C.C++ and Fortran. Although MATLAB is intended primarily for numerical computing, an optional toolbox uses the MuPAD symbolic engine, allowing access

### INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 2, Issue 1, January 2014

to symbolic computing capabilities. package, Simulink, adds graphical simulation have been done to verify the boosting feature and evaluate method.

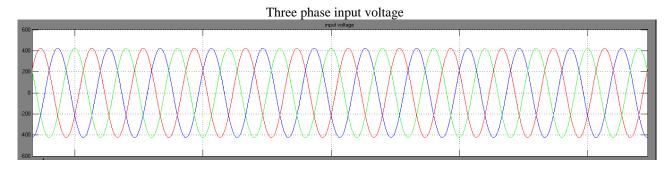

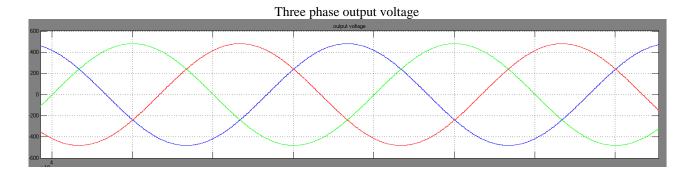

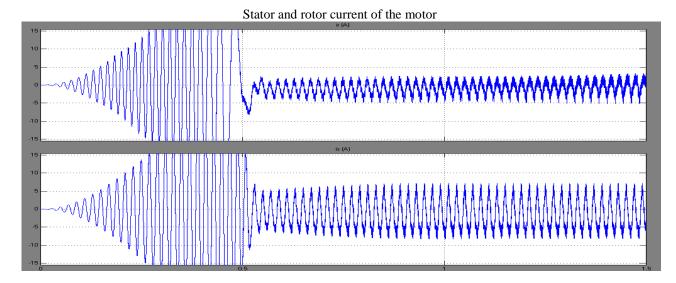

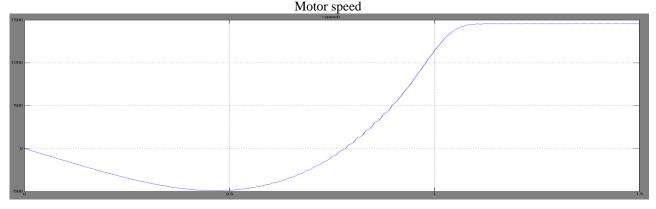

additional the output performance of the ZSMC under unbalanced multi-domain input-voltage conditions using the proposed compensation and Model-Based method. The simulation circuit of the sparse matrix Design for dynamic and embedded systems. In 2004, converter fed induction drive is shown in Fig. 5.and the MATLAB had around one million users across industry simulated results are shown in Fig. 6. Furthermore, a and academia. MATLAB users come from various current-compensation method based on an FLC has been backgrounds of engineering, science, and economics. presented to improve the output performance of the MATLAB is widely used in academic and research ZSMC. The simulation results confirm the output institutions as well as industrial enterprises. Simulations performance of the ZSMC using the current-compensation

Fig. 5. Simulation circuit for sparse matrix converter fed induction drive

Copyright to IJIREEICE www.ijireeice.com INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 2, Issue 1, January 2014

Fig. 6. Simulation results

# V. CONCLUSION

In this project the SMC and its modulation method have been presented. The ZSMC is developed based on the circuit structure of an SMC and employs the Quasi network. This unique configuration enables the Quasi ZSMC to have a voltage boost feature and high reliability with less number of the power semiconductor switches than a traditional matrix converter. Furthermore, a current-compensation method based on an FLC has been presented to improve the output performance of the SMC under unbalanced input-voltage conditions. The simulation results confirm the boosting feature and the output performance of the Quasi network based SMC under unbalanced input voltage conditions using the proposed current-compensation method.

## REFERENCES

- [1] Xia . C, "A Novel Direct Torque Control of Matrix Converter-Fed PMSM Drives Using Duty Cycle Control for Torque Ripple Reduction" pp. 2700 2713, Jun. 2014.

- [2] M. K. Nguyen, Y. G. Jung, and Y. C. Lim, "Single-Phase Z-Source AC/AC converter with wide range output voltage operation," J. of Power Electron.,vol. 9, no. 5, pp. 736–747, Oct.2013.

- [3] Kiwoo Park, Kyo-Beum Lee "Improving output performance of a Z-Source sparse matrix converter under unbalanced Input voltage conditions" IEEE Trans. Power Electron., vol. 27, No. 4, pp. 2043-2054, Apr. 2012.

- [4] Govindaraj Thangavel, Ashoke K. Ganguli and Debashis Chatterjee,"Dynamic modeling of direct drive axial flux PM LOM using FEM analysis" International journal of Elixir Electrical Engineering Vol.45 pp 8018-8022, April 2012

- [5] G. Thangavel and A. K. Ganguli,"Dynamic Modeling of Directive Drive Axial Flux PM Linear Oscillatory Machine

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 2, Issue 1, January 2014

Prototype Using FE Magnetic Analysis", Iranian Journal of Electrical and Computer Engineering, Vol. 10, No. 2, Summer-Fall 2011

[6] Govindaraj Thangavel, Debashis Chatterjee, and Ashoke K. Ganguli,"FEA based Axial Flux permanent Magnet Linear Oscillating Motor," International Journal THE ANNALS OF "DUNAREA DE JOS" UNIVERSITY OF GALATI F ASCICLE III, ELECTROTECHNICS, ELECTRONICS, AUTOMATIC CONTROL, INFORMATICS, July 2010

[7] M. Y. Lee, P. Wheeler, and C. Klumpner, "Space-vector modulated multilevel matrix converter," IEEE Trans. Ind. Electron., vol. 57, no. 10.pp. 3385–3394. Oct. 2010.

[8] S. Kim, Y. D. Yoon, and S. K. Sul, "Pulsewidth modulation method of matrix converter for reducing output current ripple," IEEE Trans. Power Electron.,vol. 25,no.10,pp.2620-2629,Oct.2010

[9] K. Park and K. B. Lee, "A Z-source sparse matrix converter under a voltage sag condition," in Proc. Energy Conver. Cong. Exposition, Sep.12–16, 2010,pp. 2893–2898.

[10] H. Karaca, R. Akkaya, and H. Dogan, "A novel compensation method based on fuzzy logic control for matrix converter under distorted input voltage conditions," presented at the Proc. EEE Electr. Mach., Vilamoura, Portugal, Sep. 2008.

[11] J.W.Kolar, F. Schafmeister, S.D. Round, and E.Hans, "Novel three-phase ac–ac sparse matrix converters," IEEE Trans. Power Electron., vol. 22,no. 5, pp.1649–1661, Sep. 2007 Developments, Chapter: 6, InTechonline Publisher.10 Oct 2012.

[12] Govindaraj Thangavel, Debashis Chatterjee, and Ashoke K. Ganguli,"Design, Development and Control of an Axial Flux Permanent Magnet Linear Oscillating Motor using FE Magnetic Analysis Simulation Models," Int. Journal of Electrical and Electronics Engineering, Oradea, Romania, October 2010

[13] Dr.T.Govindaraj, and T.Srinivasan, "An Hybrid Five-Level Inverter Topology with Single-DC Supply fed Special Electric Drive,"International Journal Of Advanced and Innovative Research.ISSN: 2278-7844, Dec-2012, pp 542-548.

[14] Dr.T.Govindaraj, and V.Purushothaman, "Simulation of Inverter Controlled BLDC Drive Using Four Switch," IJAIR.,Dec- 2012, pp 554-559.

R.Narmatha and T.Govindaraj, "Inverter Dead-Time [15] Elimination for Reducing Harmonic Distortion and Improving Power Quality", International journal of Asian Scientific Research, vol.3, April 2013 [16] Dr.T.Govindaraj, and A.Kanimozhi," Instantaneous Control of Small Inductance Brushless DC Drive,"IJAIR, Dec-2012,pp 468-474. [17] Dr.T.Govindaraj, and T.Keerthana," DFC And DTC Of Special Electric Drive Using PI And FLC, "IJAIR, Dec-2012 ,pp 475-481. [18] Dr.T.Govindaraj, and T.Sathesh kumar, "New Efficient Cuk Converter Fed PMDC Drive For Applications," IJAIR, Dec- 2012, pp 518-523

[19]Dr.T.Govindaraj, and B.Gokulakrishnan, "Simulation of PWM based AC/DC Converter control to improve Power Quality," International Journal of Advanced and Innovative Research.ISSN: 2278-7844, Dec-2012, pp 524-533.

[20] T.Govindaraj, Rasila R,"Development of Fuzzy Logic Controller for DC – DC Buck Converters", International Journal of Engineering Techsci Vol 2(2), 192-198, 2010

[21]Govindaraj Thangavel, Debashis Chatterjee, and Ashoke K. Ganguli," Design, Development and Finite Element Magnetic Analysis of an Axial Flux PMLOM," International Journal of Engineering and Technology, Vol.2 (2), 169-175, 2010.

# BIOGRAPHY

**Dr.Govindaraj Thangavel** born in Tiruppur, India, in 1964. He received the B.E. degree from Coimbatore Institute of Technology, M.E. degree from PSG College of Technology and Ph.D. from Jadavpur University, Kolkatta, India in 1987, 1993 and 2010 respectively. His Biography is included in Who's Who in Science and Engineering 2011-2012 (11th Edition). Scientific Award of Excellence 2011

from American Biographical Institute (ABI). Outstanding Scientist of The 21st century by International Biographical centre of Cambridge, England 2011.

Since July 2009 he has been Professor and Head of the Department of Electrical and Electronics Engineering, Muthayammal Engineering College affiliated to Anna University, Chennai, India. His Current research interests includes Permanent magnet machines, Axial flux Linear oscillating Motor, Advanced Embedded power electronics controllers, finite element analysis of special electrical machines, Power system Engineering and Intelligent controllers.He is a Fellow of Institution of Engineers India(FIE) and Chartered Engineer (India). Senior Member of International Association of Computer Science and Technology (IACSIT). Information. Member International Association of Engineers(IAENG), Life of Indian Member Society for Technical Education(MISTE). Ph.D. Recognized Research Supervisor for Anna University and Satyabama University Chennai Editorial Board Member for journals like International Journal of Computer and Electrical Engineering, International Journal of Engineering and Technology, International Journal of Engineering and Advanced Technology (IJEAT).International Journal Peer Reviewer for Taylor &Francis International "Electrical Power Components & System"United Kingdom, Journal of Electrical and Electronics Engineering Research, Journal of Engineering Technology Research (JETR), International Journal of the Physical Sciences, Association for the Advancement of Modelling and Simulation Techniques Enterprises, International Journal of Engineering Computer Science (IJECS), Scientific Research and Essays, Journal of Engineering and Computer Innovation,E3 Journal of Energy Oil and Research, World Academy of Science, Engineering and Technology, Journal of Electrical and Control Engineering ( JECE), Applied Computational Electromagnetics Society etc.. He has published 132 research papers in International/National Conferences Journals. Organized 40 National International Conferences/Seminars/Workshops. Received Best paper award for ICEESPEEE 09 conference paper. Coordinator Sponsored SDP on Soft Computing AICTE Techniques In Advanced Special Electric Drives, 2011. Coordinator for AICTE Sponsored National Seminar on Computational Intelligence Techniques in Green Energy, 2011. Chief Coordinator and Investigator for AICTE sponsored MODROBS - Modernization of Electrical Machines Laboratory. Coordinator for AICTE Sponsored International Seminar on "Power Quality Issues in Renewable Energy Sources and Hybrid Generating System", July 2013.