INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 3, Issue 3, March 2015

# A Detailed Review on Architectures for 2-DWT by using Radix-4 Booth Multiplier

Mr. Hemantkumar H. Nikhare<sup>1</sup>, Prof. Ashish Singhadia<sup>2</sup>

Scholar, Electronics & Tele, VIT, Bhopal, India<sup>1</sup>

Professor, Electronics & Tele, VIT, Bhopal, India<sup>2</sup>

**Abstract:** The aim of this paper is to give a review of VLSI architectures for 2-DWT implementation of wavelet transform by using 4 Booth multiplier. This review paper describes implementation of radix-4 Modified Booth Multiplier and this implementation is compared with Radix-2 Booth Multiplier. Modified Booth's algorithm employs both addition and subtraction and also treats positive and negative operands uniformly. Parallel MAC is frequently used in digital signal processing and video/graphics applications. A new architecture of multiplier and accumulator (MAC) for high speed arithmetic by combining multiplication with accumulation and devising a carry-look ahead adder (CLA), the performance is improved. Modified Booth multiplication. Designing of this algorithm is done by using VHDL and simulated using Modelsim SE 16.3f software has been used and implemented on Matlab R2013b. This paper proposes the design and implementation of Booth multipliers. We can achieve the Experimental results demonstrate that the modified radix 4 Booth multiplier has 22.9% power reduction than the conventional radix 2 Booth Multiplier and near about 50% power reduction than the conventional Normal Booth Multiplier

**Keywords**: Discrete Wavelet Transform (DWT), VLSI architectures, image compression.VLSI, Carry Select Adder (CSA), Carry Look Ahead Adder (CLA), ASM, MAC, Modelsim SE 16.3f, Matlab R2013b.

# **1. INTRODUCTION**

The Discrete Wavelet Transform (DWT) plays a major role in the fields of signal analysis, computer vision, object recognition, image compression and video compression standard. The advantage of DWT over other traditional transformations is that it performs multi resolution analysis of signals with localization both in time and frequency. At present, many VLSI architectures for the 2-D DWT have been proposed to meet the requirements of real-time processing. The implementation of DWT in practical system has issues. First, the complexity of wavelet transform is several times higher than that of DCT. Second, DWT needs extra memory for storing the intermediate computational results. Moreover, for real time image compression, DWT has to process massive amounts of data at high speeds. The use of software implementation of DWT image compression provides flexibility for manipulation but it may not meet timing constraints in certain applications. First, is that the high cost of hardware implementation of multipliers. Such implementations require both large number of arithmetic computations and storage, which are not desirable for either high speed or low power image / video processing. Therefore a new approach called the lifting scheme based wavelet transform was proposed by Matlab. based on a spatial construction of the second generation. The lifting scheme has many advantages over the previous approaches. In particular, all the interesting properties of wavelets, coefficients. As a consequence, it is easier to design wavelet filters. Unlike convolutional wavelets, lifting scheme does not depend on Fourier transform of the wavelets. As a consequence, wavelets can be designed on arbitrary lattices in spatial domain. Since the lifting

scheme makes optimal use of similarities between the high and low pass filters to speed up the calculation of wavelet transform, it has been adopted in the image compression standard JPEG2000. The various architectures differ in terms of required numbers of the multipliers, adders and registers, as well as the amount of accessing external memory, and leads to decrease efficiently the hardware cost and power consumption of design.Inspite of improving the efficiency of existing architectures, the present requirement is to improve hardware utilization and capable of handling multiple data streams for the calculation of 2D DWT. This paper focuses to give brief survey on 2D DWT hardware architectures with their implementation VLSI structures and computational complexities. In various one-dimensional lifting-based DWT architectures suitable for VLSI implementation and comparison of the hardware and timing complexities of all the architecture. gives the memory requirement for 2-DWT followed dimensional architectures, by representative architectures and a comparison of their hardware and timing complexities with the possibility of extending to multilevel input signals[7].

Fig.1. Block diagram flow of a traditional 2-D DWT [2].

# 2. NORMAL BOOTH MULTIPLIER

In many real-time DSP applications, high performance is a critical concern. Multiplication is the most fundamental arithmetic operation used in most of the signal processing

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL. ELECTRONICS. INSTRUMENTATION AND CONTROL ENGINEERING Vol. 3, Issue 3, March 2015

algorithms. But multipliers usually have large area, larger 2 Carry propagation delay increases linearly with bit delay and consume more power. However, achieving this length as next stage output is dependent on previous stage may be done at the cost of area, on chip power consumed output. and delays. In the binary number system the digits, called bits, are limited to the set  $\{0, 1\}$ . The result of multiplying any binary number by a binary bit is either 0, or the original number. This makes formation of the intermediate partial-products simple and efficient. Adding all these partial-products is time consuming task for any binary multipliers. The entire process consists of three steps partial product generation, partial product reduction and addition of partial products as shown in Fig 1. But in Recoding scheme used in radix-2 booth multiplier booth multiplication, partial product generation is done is show in the Table 1. based on recoding scheme e.g. radix 2 encoding. Bits of Table 1 Recoding Table for Booth Multiplier [16] multiplicand (Y) are grouped from left to right and corresponding operation on multiplier (X) is done in order generate the partial product. In radix-2 booth multiplication partial product generation is done based on encoding which is as given by Table1. Parallel

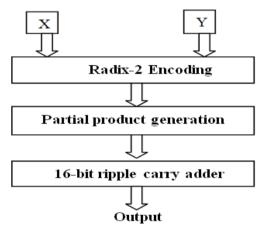

Fig. 2. Flow chart for Normal Booth Multiplier [16]

Multiplication using normal Booth's recoding algorithm technique based on the fact that partial product can be generated for group of consecutive 0"s and 1"s which is called Booth's recoding. This recoding algorithm is used to generate efficient partial product. These partial products always have large number of bits than the input number of bits. This increase in the width of partial product usually depends upon the radix scheme used for recoding. So, these scheme uses less partial product generation which in turn provides low power and area but in the Normal Booth multiplier Ripple Carry Adder is used shown in Fig[19].

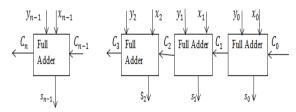

Fig. 3. Block Diagram of RCA (Ripple Carry adder)

# 2.1 Drawbacks of using Ripple Carry Adder:

1 It is not efficient when large numbers of bits are used.

#### 2.2 Logic equations:-

| Ci = xi & yi        |                       | (1) |

|---------------------|-----------------------|-----|

| $Pi = xi \wedge yi$ |                       | (2) |

| Si = Pi ^ Ci        |                       | (3) |

| whe                 | re Pi=Partial product |     |

|                     | Ci=Carry bit          |     |

| Qn | Qn+1 | Recoded<br>Bits | Operation  |

|----|------|-----------------|------------|

| 0  | 0    | 0               | Shift      |

| 0  | 1    | +1              | Add X      |

| 1  | 0    | -1              | Subtract X |

| 1  | 1    | 0               | Shift      |

Hardware implementation of Booth Algorithm requires the register configuration. So named the Multiplier and Multiplicand as registers 'A', 'B' and 'O' as AC, BR as shown in Complete flow chart 2. An extra flip flop is Qn+1 is added to provide a double bit inspection of the multiplier. The complete fig 3 has shown condition basis implementation of the Radix-2 Booth Algorithm[16].

#### **3. RADIX-2 BOOTH MULTIPLIER**

The Booth algorithm was invented by A. D. Booth, forms the base of Signed number multiplication algorithms that are simple to implement at the hardware level, and that have the potential to speed up signed multiplication Considerably. Booth's algorithm is based upon recoding the multiplier, y, to a recoded, value, z, leaving the multiplicand, x, unchanged. In Booth recoding, each digit of the multiplier can assume negative as well as positive and zero values. There is a special notation, called signed digit (SD) encoding, to express these signed digits. In SD encoding +1 and 0 are expressed as 1 and 0, but -1 is expressed as 1 (Vincent P. Heuring, 2003). The value of a 2s complement integer was defined a by equation 1.

$$y = -y_{m-1} \ 2^{m-1} + \sum_{i=0}^{m-2} y_i 2^i \qquad \dots \qquad (1)$$

This equation says that in order to get the value of a signed 2's complement number, multiply the  $m - i^{th}$  digit by -2`-1, and multiply each remaining digit i by +2g. For example, -7, which is 1001 in 2's complement notation, would be, in SD notation, 1001 = -8 + 0 + 0 + 1 = -7. For implementing booth algorithm most important step is booth recoding. By booth recoding we can replace string of 1s by 0s. For example the value of strings of five 1s,  $11111 = 2^5 - 1 =$ 100001 = 32 - 1 = 31. Hence if this number were to be used as the multiplier in a multiplication, we could replace five additions by one addition and one subtraction.

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 3, Issue 3, March 2015

The Booth recoding procedure, then, is as follows:

1. Working from LSB to MSB, replace each 0 digit of the original number with a 0 in the recoded number until a 1 is encountered.

2. When a 1 is encountered, insert a 1 at that position in the recoded number, and skip over any succeeding I's until a 0 is encountered.

3. Replace that 0 with a 1 and continue. This algorithm is expressed in tabular form in Table 1, considering pairs of numbers,  $y_{i-1}$  and  $y_i$  and the recoded digit,  $z_i$ . as shown in Table 1.

Table 2: Booth recoding table for radix-2 [11].

| $y_i$ | $y_{i-1}$ | $z_{i-1}$ | Multiplier<br>Value | Situation               |

|-------|-----------|-----------|---------------------|-------------------------|

| 0     | 0         | 0         | 0                   | String of 0s            |

| 0     | 1         | 1         | +1                  | End of string<br>of 1 s |

| 1     | 0         | 1         | -1                  | Begin string<br>of 1s   |

| 1     | 1         | 0         | 0                   | string of 1s            |

# **3.1 BOOTH ALGORITHM:**

1. Add 0 to right of LSB of multiplier and look at rightmost of multiplier to make pairing of 2 bits from right to left and mark corresponding multiplier value as shown in fig. 1

2.00 or11:do nothing.

3. 01: Marks the end of a string of 1s and add multiplicand to partial product (running sum)

4. 10: Marks the beginning of a string of 1s substract multiplicand from partial product.

one of the solution realizing high sped multipliers is to enhance parallelism which helps in decreasing the number of subsequent calculation stages. The original version of booth's multiplier (radix-2) had two drawbacks.

1. The number of add / subtract operation became varible and hence became inconvenient while designing Parallel multipliers.

2. The Algorithm becomes inefficient when there are isolated 1s.

These Problem are overcome by using Radix-4 Booth algorithm which can scan string of three. This booth multiplier technique is to increase speed by reducing the number of partial product by half [11].

# 4. ARCHITECTURE OF RADIX-4 BOOTH MULTIPLIER:

Multipliers are the essential components in real time signal processing and also for all the multimedia applications. Many previous works were done in implementing highspeed multiplier to reduce power consumption . This is due to the increased demand for portable multimedia applications which require low power consumption as well as high speed operation. However low-power multipliers without any consideration for high-speed are not the appropriate solutions of low-energy embedded signal processing for multimedia applications. Previously, a hybrid radix-4 modified Booth encoded (MBE) multiplier

was proposed for low-power and high-speed operation. This multiplier architecture had separate radix-4. Both encoders were operated regardless of the input patterns, resulting in power and area overhead.

Therefore although its power consumption was reduced compared to the radix-4 architecture, its critical path delay was considerably increased. As a result, its energy efficiency was not improved over conventional radix-4.

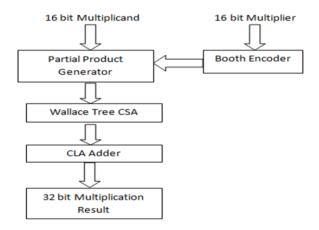

We propose a multiplier that computes the partial product and parallely performs the accumulation of the partial products. This multiplier operates on the Modified Booth Encoder algorithm and the Wallace tree in radix-4 mode. In the majority of the input cases, the radix-8 architecture is as fast as radix-4 architecture while consuming less power.

However, in the remaining input cases, the radix-8 architecture is bottlenecked by the generation of the  $\pm 3B$  partial product term, which requires an additional carry propagation adding stage. Therefore, we use radix-4 multiplier, which is faster at its operation and the cost of power increases. The structure of the proposed multiplier is illustrated in figure 1[15].

Fig. 4. Architecture of Radix-4 multiplier [13].

# 5. RADIX-4 MODIFIED BOOTH ALGORITHM

The modified Booth algorithm minimises the number of partial products by half. We used the modified Booth encoding (MBE) scheme . It is known as the most efficient Booth encoding and decoding scheme. To multiply, multiplicand 'X' by multiplier 'Y' using the modified Booth algorithm.

First group the multiplier bits 'Y' by three bits and encoding into one of {-2, -1, 0, 1, 2}. Prior to convert the multiplier, a zero is appended into the Least Significant Bit (LSB) of the multiplier. Table I shows the rules to generate the encoded signals by MBE scheme and Fig. 2 (a) shows the corresponding logic diagram.

The Booth decoder generates the partial products using the encoded signals[11].

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 3, Issue 3, March 2015

Fig. 5. Basic arithmetic steps of multiplication and accumulation[9],[10].

Fig. 6. Booth Recoding [10].

Table 3 : Radix 4 Booth Table [10]

| Select Line | <b>Partial Products (Operation)</b> |  |  |  |  |  |

|-------------|-------------------------------------|--|--|--|--|--|

| (Encoding)  |                                     |  |  |  |  |  |

| 000         | Add 0                               |  |  |  |  |  |

| 001         | Add multiplicand                    |  |  |  |  |  |

| 010         | Add multiplicand                    |  |  |  |  |  |

| 011         | Add 2* multiplicand                 |  |  |  |  |  |

| 100         | Subtract 2* multiplicand            |  |  |  |  |  |

| 101         | Subtract multiplicand               |  |  |  |  |  |

| 110         | Subtract multiplicand               |  |  |  |  |  |

| 111         | Subtract 0                          |  |  |  |  |  |

The recoding is done by appending one zero to the Least Significant Bit (LSB) and extending the Most Significant Bit (MSB) with the sign bit if necessary. Then the grouping of 3 bits from the LSB is done as shown in Fig 2. The obtained result is -1 - 1 0 - 2. This result is multiplied with the multiplier and the number of partial product is reduced [10].

One of the solutions of realizing high speed multipliers is to enhance parallelism which helps to decrease the number of subsequent calculation stages. The original version of the Booth algorithm (Radix-2) had two drawbacks. They are:

(i) the number of add subtract operations and the number ofshift operations become variable and become inconvenient in designing parallel multipliers.

(ii) The algorithm becomes inefficient when there are isolated 1's. These problems are overcome by using modified Radix-4 Booth multiplication algorithm.

Booth algorithm which scans strings of three bits is given below:

1) Extend the sign bit 1 position if necessary to ensure that n is even.

2) Append a 0 to the right of the LSB of the multiplier.

3) According to the value of each vector, each Partial Product will be 0, +M, -M, +2M or -2M.

The negative values of B are made by taking the 2's complement and in this paper Carry-look-ahead (CLA) fast adders are used. The multiplication of M is done by shifting M by one bit to the left. Thus, in any case, in designing n-bit parallel multiplier, only n/2 partial products are produced.

The partial products are calculated according to the following rule.

$$Z_n = -2 \times B_{n+1} + B_n + B_{n-1} \dots \dots \dots (1)$$

#### where B is the multiplier

#### Consider example for radix 4:

|             |   | 2011 | Siuci           | Crann | <i>ne</i> 10    | 1 1 40 |    | т.                 |

|-------------|---|------|-----------------|-------|-----------------|--------|----|--------------------|

| A           |   |      | 01              | 00    | 01              |        |    | 17                 |

| X           | × |      | 11              | 01    | 11              |        |    | -9                 |

| Y           |   |      | $0\overline{1}$ | 10    | $0\overline{1}$ |        |    | recoded multiplier |

|             |   |      | -A              | +2A   | -A              |        |    | operation          |

| Add $-A$    | + |      | 10              | 11    | 11              |        |    |                    |

| 2-bit Shift |   | 1    | 11              | 10    | 11              | 11     |    |                    |

| Add $2A$    | + | 0    | 10              | 00    | 10              |        |    |                    |

|             |   |      | 01              | 11    | 01              | 11     |    |                    |

| 2-bit Shift |   |      | 00              | 01    | 11              | 01     | 11 |                    |

| Add $-A$    | + |      | 10              | 11    | 11              |        |    |                    |

|             |   |      | 11              | 01    | 10              | 01     | 11 | -153               |

|             |   |      |                 |       |                 |        |    |                    |

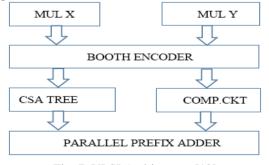

## 6. VLSI ARCHITECTURE IMPLEMENTATION

The architecture of the proposed ECAT Booth multiplier is designed by using tree-based carry save reduction followed by parallel-prefix carry-propagate addition architecture. The whole architecture of the proposed ECAT Booth multiplier is shown in Fig.accumulator. In final adder both sum and carry is added to produce the 2N bits product.

Fig. 7. VLSI Architecture [10].

# 7. 2-D DISCRETE WAVELET TRANSFORM

The main challenges in the hardware architectures for 1-D DWT are the processing speed and the number of multipliers and adders while for 2-D DWT it is the memory issue that dominates the hardware cost and the architectural complexity. A 2-D DWT is a separable transform where 1-D wavelet transform is taken along the rows and then a 1-D wavelet transform along the columns. The 2-D DWT operates by inserting array

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL. ELECTRONICS. INSTRUMENTATION AND CONTROL ENGINEERING Vol. 3, Issue 3, March 2015

transposition between the two 1-D DWT. The rows of the embedded internal buffer are considered the most critical array are processed first with only one level of issues for the implementation of 2D-DWT. As the cache is decomposition. This essentially divides the array into two used to reduce the main memory access in the general vertical halves, with the first half storing the average processor architectures, in similar way, the internal buffer coefficients, while the second vertical half stores the detail is used to reduce the external memory access for 2Dcoefficients. This process is repeated again with the DWT. However, the internal buffer would occupy much columns, resulting in four sub-bands within the array area and power consumption. Three main architecture defined by filter output.as in three-level decomposition.

The LL sub-band represents an approximation of the aim to implement efficiently the 2D-DWT level by level, original image, the LL1 sub-band can be considered as a line-based and block based architectures. Intermediate 2:1 sub-sampled version of the original image. The other values between row and column processing are stored in three sub-bands HL1,LH1, and HH1 contain higher memory. Since this memory must be large enough to keep frequency detail information. This process is repeated for wavelet coefficients for the entire image, external memory as many levels of decomposition as desired. The is usually used. Access to the external memory is JPEG2000 standard specifies five levels of decomposition, sometimes done in row-wise order, and sometimes in although three are usually considered acceptable in column-wise order, so high-bandwidth access modes hardware.

JPEG2000, two points have to be taken into account.

Firstly, the 1-D DWT generates the control signal memory to compute 2-D DWT and manages the internal memory access. Secondly, we need to store temporary results A multiplier can be divided into three operational steps: generated by 2-D column filter. The amount of the i. Radix-4 Booth algorithm in which a partial product is external memory access and the area occupied by the generated.

design approaches were proposed in the literature with the cannot be used. 157 external memory access can become In order to extend the 1-D filter to compute 2-D-DWT in the performance bottleneck of the system for the given J level of decomposition [7].

### 8. ARCHITECTURE OF A MULTIPLIER

| Architecture                      | Multiplie-<br>rs/<br>Shifters | Adders | Memory            | Compu-ting<br>Time                    | Out-<br>put<br>Late<br>-ncy | DWT<br>Mode | HUE<br>% | Bound-<br>ary<br>Proces-<br>sing | Control<br>Comple-<br>xity |

|-----------------------------------|-------------------------------|--------|-------------------|---------------------------------------|-----------------------------|-------------|----------|----------------------------------|----------------------------|

| Wu[1]                             | 16                            | 16     | N <sup>2</sup> /4 | $2N^2(1-4^J)/3$ of                    | 2N                          | СВ          | 100      | ZP                               |                            |

| <sup>(5,3)</sup><br>(9,7)         | 32                            | 32     | N <sup>2</sup> /4 | $2N^{2}(1-4)/3$                       | 4N                          | СВ          | 100      | ZP                               | Medium                     |

| Liao+RA[11,2                      | 4                             | 8      | 0                 | $N^2$                                 | 2N                          | LB          | 66.7     | ZP                               |                            |

| <sup>8]</sup><br>(5, 3)<br>(9, 7) | 12                            | 16     | 0                 | N <sup>2</sup>                        | 4N                          | LB          | 66.7     | ZP                               | Complex                    |

| Barua[10] (5, 3                   | 4                             | 8      | N <sup>2</sup> /4 | $2N^{2}(1-4^{J})/3$                   | 5N                          | LB          | 100      | EBDE                             | Simple                     |

| (9, 7)                            | 12                            | 16     | N <sup>2</sup> /4 | 2N <sup>2</sup> (1-4 <sup>J</sup> )/3 | 7N                          | LB          | 100      | EBDE                             |                            |

| Andra [8]                         | 4                             | 8      | 0                 | $2N^{2}(1-4^{J})/3$                   | 2N                          | LB          | 100      | SSO                              | Medium                     |

| (9, 7)                            | 6                             | 8      | 0                 | $4N^{2}(1-4)/3$                       | N <sup>2</sup> /4           | LB          | 100      | SSO                              |                            |

| FA [29]                           | 4                             | 8      | N <sup>2</sup> /4 | $2N^{2}(1-4^{J})/3$                   | N <sup>2</sup> /4           | LB          | 100      | EBDE                             |                            |

| <sup>(5,3)</sup><br>(9,7)         | 10                            | 16     | N <sup>2</sup> /4 | $2N^{2}(1-4)/3$                       | N <sup>2</sup> /4           | LB          | 100      | EBDE                             | Simple                     |

|                                   |                               |        |                   | _                                     |                             |             |          |                                  |                            |

| FA[19]<br>XinTian[20]             | 1 shifters                    | 2      | N <sup>2</sup> /4 | ]N <sup>2</sup> /4                    | N <sup>2</sup>              | LB          | 100      | EBDE                             | Simple                     |

| MIMOA<br>(M=2)                    | 8                             | 16     | N <sup>2</sup> /2 | N <sup>2</sup> /M                     | М                           | LB          | 100      | Not<br>discussed                 | Simple                     |

| MIMOA<br>(M=8)                    | 32                            | 64     | N <sup>2</sup> /8 | N <sup>2</sup> /M                     |                             |             |          | arseussed                        |                            |

Table 4: Literature Review of 2-D DWT architectures

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL. ELECTRONICS. INSTRUMENTATION AND CONTROL ENGINEERING Vol. 3. Issue 3. March 2015

ii. Carry save adder and Accumulator

iii. The final addition in which the final multiplication result is produced by adding the sum and the carry

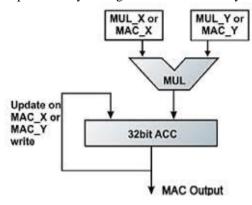

Fig. 8: MAC Multiplier[9].

Generally if N-bit data of multiplicand 'X' is multiplied with N-bit multiplier 'Y' then it generates N- partial [8] products. But if Radix-4 booth algorithm is used then number of partial products will be reduced to N/2. In addition, the signed multiplication based on 2's complement numbers is also possible.

$$X = -2^{N-1}x_{N-1} + \sum_{i=0}^{N-1} x_i 2^i, \quad x_i \in 0, 1....(1)$$

Where  $di = -2x_{2i+1} + x_{2i} + x_{2i-1}$

$$P = X \times Y + Z = \sum_{i=0}^{N/2-1} di \, 2^i Y + \sum_{j=0}^{2N-1} zi \, 2^i \dots (3)$$

In CSA, the sign extension is used in order to increase the bit density of the operands. Half adder is used to generate sum and carry in CSA. The generated carry is stored in [13] Bodasingi Vijay Bhaskar, Valiveti Ravi Tejesvi, Reddi Surya accumulator [9].

#### 9. CONCLUSION

Transform dimensional Discrete Wavelet image compression process by using the Radix 4-booth multiplier designed using VHDL and computational time [15] for the DWT architectures using Matlab and Modelsim6.3f Software. This review paper is useful for explaining a new method of 2-D DWT architectures by using 4 Booth multiplier capable of compressing image suitable for application in image and video processing multimedia real time applications.

#### REFERENCES

- [1] Wei Zhang, Member, IEEE, Zhe Jiang, Zhiyu Gao, and Yanyan Liu, "An Efficient VLSI Architecture for Lifting-Based Discrete Wavelet Transform" IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS, VOL. 59, NO. 3, MARCH 2012.

- [2] Chih-Hsien Hsia, Member, IEEE, Jen-Shiun Chiang, Member, IEEE, and Jing-Ming Guo, Senior Member, IEEE "Memory-Efficient Hardware Architecture of 2-D Dual-Mode Lifting-Based Discrete Wavelet Transform" IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS FOR VIDEO TECHNOLOGY, VOL. 23, NO. 4, APRIL 2013.

- Yeong-Kang Lai, Member, IEEE, Lien-Fei Chen, Student Member. [4] IEEE, and Yui-Chih Shih, "A High-Performance and Memory-Efficient VLSI Architecture with Parallel Scanning Method for 2-D Lifting Based Discrete Wavelet Transform" IEEE Transactions on Consumer Electronics, Vol. 55, No. 2, MAY 2009 Contributed Paper.

- [5] Basant Kumar Mohanty, Senior Member, IEEE, and Pramod Kumar Meher, Senior Member, IEEE," Memory-Efficient High-Speed Convolution-based Generic Structure for Multilevel 2-D DWT" IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS FOR VIDEO TECHNOLOGY, VOL. 23, NO. 2, FEBRUARY 2013.

- Yusong Hu, Student Member, IEEE, and Ching Chuen Jong, [6] Member, IEEE, "A Memory-Efficient High-Throughput Architecture for Lifting-Based Multi-Level 2-D DWT" IEEE TRANSACTIONS ON SIGNAL PROCESSING, VOL. 61, NO. 20, OCTOBER 15, 2013..

- [7] Usha Bhanu.N and Dr.A. Chilambuchelvan, "A Detailed Survey on VLSI Architectures for Lifting based DWT for efficient hardware implementation" International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.2, April 2012.

- S. Shafiulla Basha1, Syed. Jahangir Badashah," DESIGN AND IMPLEMENTATION OF RADIX-4 BASED HIGH SPEED MULTIPLIER FOR ALU'S USING MINIMAL PARTIAL PRODUCTS" International Journal of Advances in Engineering & Technology, July 2012. ©IJAET ISSN: 2231-1963.

- [9] G. Java Prada, N.C. Pant "Design and Verification of faster Multiplier", vol. 1 issue 3, pp. 683-686, ISSN: 2248-9622. Vol. 1, Issue 3, pp.683-686.

- [10] M. Gopinathan & D. Jessintha (2013) "An Error Compensated DCT Architecture with Booth Multiplier", IJAEEE- ISSN: 2278-8948, Volume-2, Issue-4, 2013.

- [11] Sukhmeet Kaur, Suman and Manpreet Signh Manna," Implementation of Modified Booth Algorithm (Radix 4) and its Comparison with Booth Algorithm (Radix-2)" Advance in Electronic and Electric Engineering. ISSN 2231-1297, Volume 3, Number 6 (2013), pp. 683-690.

- [12] K. Babulu, G. Parasuram, "FPGA Realization of Radix-4 Booth Multiplication Algorithm for High Speed Arithmetic Logics" (IJCSIT) International Journal of Computer Science and Information Technologies, Vol. 2 (5) , 2011, 2102-2107, ISSN-0975-9646

- Implementation of Radix-4 Multiplier with a Prakash Rao." Parallel MAC unit using MBE Algorithm" International Journal of Advanced Research in Computer Engineering & Technology (IJARCET) Volume 1, Issue 5, July 2012, ISSN: 2278-1323.

- In this paper, we have trying to achieved the 2- [14] P.Ramesh , A.Deepthi, K.Sowjanya," Implementation of Discrete Wavelet Transform on FPGA to Detect Electrical Power System Disturbances" International Journal Of Engineering And Computer Science ISSN:2319 7242 Volume 2 Issue 11 November, 2013 Page No. 3223-3227.

- S. JAGADEESH, S.VENKATA CHARY, " Design of Parallel Multiplier-Accumulator Based on Radix-4 Modified Booth Algorithm with SPST" International Journal Of Engineering Research And Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 2, issue 5, September-October 2012, pp.425-431.

- [16] Sakshi Rajput, Priya sharma, Gitanjali and Garima, " High Speed and Reduced Power -Radix-2 Booth Multiplier" (IJCEM) International Journal of Computational Engineering & Management, Vol. 16 Issue 2, March 2013 ISSN (Online): 2230-7893.

- [17] Nishat Bano, "VLSI Design of Low Power Booth Multiplier" International Journal of Scientific & Engineering Research, Volume 3, Issue 2, February -2012 1 ISSN 2229-5518.

#### BIOGRAPHY

Mr. Hemantkumar H. Nikhare M. Tech. (Digital & Communication.) Scholar in Vedica Institute of Technology Bhopal, under R.G.P.V. Bhopal. And Completed B.E. (Electronics Engg.) from Rajiv Gandhi College of Engineering, Research & Technology Chandrapur under R.T.M. Nagpur University.